樹(shù)脂黑板技術(shù)、價(jià)格與行業(yè)服務(wù)網(wǎng)絡(luò)綜合分析

樹(shù)脂黑板作為一種現(xiàn)代化的書(shū)寫工具,憑借其耐用、易清潔和高對(duì)比度的特點(diǎn),在教育、辦公及商業(yè)展示領(lǐng)域得到了廣泛應(yīng)用。本文將從樹(shù)脂黑板的技術(shù)特性、價(jià)格因素、行業(yè)用戶關(guān)注要點(diǎn)以及服務(wù)網(wǎng)絡(luò)建設(shè)等方面展開(kāi)分析。

一、樹(shù)脂黑板技術(shù)概述

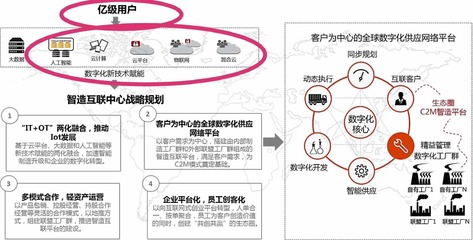

樹(shù)脂黑板采用高分子樹(shù)脂材料制成,表面經(jīng)過(guò)特殊處理,具有抗沖擊、防潮、耐磨損等優(yōu)勢(shì)。與傳統(tǒng)黑板相比,樹(shù)脂黑板書(shū)寫流暢,粉塵少,且支持磁性吸附功能,便于多媒體教學(xué)和會(huì)議展示。部分高端產(chǎn)品還結(jié)合了網(wǎng)絡(luò)技術(shù)服務(wù),如智能互聯(lián)和遠(yuǎn)程控制,進(jìn)一步提升了使用體驗(yàn)。

二、價(jià)格因素及行業(yè)用戶關(guān)注點(diǎn)

樹(shù)脂黑板的價(jià)格受多種因素影響,包括材質(zhì)等級(jí)、尺寸規(guī)格、功能集成度以及品牌溢價(jià)。行業(yè)用戶(如學(xué)校、企業(yè))在選購(gòu)時(shí)通常關(guān)注以下因素:

- 耐用性與維護(hù)成本:用戶傾向于選擇壽命長(zhǎng)、維護(hù)簡(jiǎn)單的產(chǎn)品,以降低長(zhǎng)期使用成本。

- 環(huán)保與健康:無(wú)毒、低粉塵的樹(shù)脂材料更受青睞,尤其在教育領(lǐng)域。

- 性價(jià)比:用戶會(huì)綜合考慮初始價(jià)格與功能,尋求最佳平衡點(diǎn)。

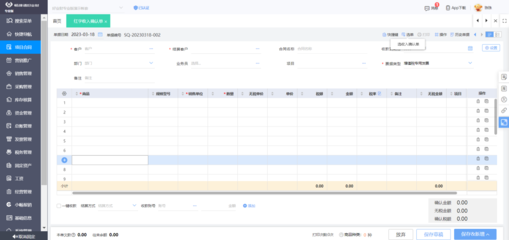

- 技術(shù)服務(wù)支持:包括安裝、培訓(xùn)和售后,確保產(chǎn)品高效運(yùn)行。

三、公司服務(wù)網(wǎng)絡(luò)與網(wǎng)絡(luò)技術(shù)服務(wù)

為了滿足用戶需求,企業(yè)需建立完善的服務(wù)網(wǎng)絡(luò),覆蓋銷售、安裝和維護(hù)環(huán)節(jié)。這包括:

- 本地化服務(wù)點(diǎn):在重點(diǎn)區(qū)域設(shè)立服務(wù)網(wǎng)點(diǎn),提供快速響應(yīng)。

- 線上支持平臺(tái):通過(guò)網(wǎng)站或應(yīng)用程序,提供產(chǎn)品咨詢、故障排查和遠(yuǎn)程協(xié)助。

- 網(wǎng)絡(luò)技術(shù)集成:利用物聯(lián)網(wǎng)和云計(jì)算,實(shí)現(xiàn)智能黑板的數(shù)據(jù)同步和更新,例如通過(guò)云服務(wù)進(jìn)行內(nèi)容管理和協(xié)作。

四、總結(jié)與展望

樹(shù)脂黑板行業(yè)正朝著智能化、環(huán)保化方向發(fā)展。價(jià)格合理、技術(shù)先進(jìn)且服務(wù)網(wǎng)絡(luò)健全的產(chǎn)品將更受市場(chǎng)歡迎。企業(yè)應(yīng)持續(xù)優(yōu)化技術(shù),加強(qiáng)網(wǎng)絡(luò)服務(wù),以提升用戶體驗(yàn)和競(jìng)爭(zhēng)力。隨著5G和AI技術(shù)的融入,樹(shù)脂黑板有望成為智慧教育和辦公的核心工具之一。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.zhuangde.com.cn/product/39.html

更新時(shí)間:2026-04-06 12:57:40